## IOWA STATE UNIVERSITY Digital Repository

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2015

# Power conversion techniques in nanometer CMOS for low-power applications

Wei Fu Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Fu, Wei, "Power conversion techniques in nanometer CMOS for low-power applications" (2015). *Graduate Theses and Dissertations*. 14307. https://lib.dr.iastate.edu/etd/14307

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

## Power conversion techniques in nanometer CMOS for low-power

## applications

by

## Wei Fu

A dissertation submitted to the graduate faculty

in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

Major: Electrical Engineering

Program of Study Committee: Ayman Fayed, Major Professor Nathan Neihart Chris Chu Liang Dong Yong Guan

Iowa State University

Ames, Iowa

2015

Copyright © Wei Fu, 2015. All rights reserved.

www.manaraa.com

## TABLE OF CONTENTS

ii

| LIST OF TABLES<br>LIST OF FIGURES                         | iv<br>v |

|-----------------------------------------------------------|---------|

| ABSTRACT                                                  | x       |

| CHAPTER 1. INTRODUCTION                                   | 1       |

| 1.1 Basics on Power Conversion Schemes                    | 3       |

| 1.2 Two-Step Power Conversion Schemes                     | 9       |

| 1.2.1 Fully-Integrated Linear Regulators                  | 11      |

| 1.2.2 Fully-Integrated Switching Regulators               | 13      |

| 1.3 One-Step Power Conversion Schemes                     | 16      |

| 1.4 Thesis Organization                                   | 18      |

| 1.5 References                                            | 21      |

| CHAPTER 2. ANALYSIS AND MODELING OF LOSSES IN LOW-        |         |

| POWER BUCK REGULATORS                                     | 26      |

| 2.1 Switching Losses Analysis                             | 30      |

| 2.1.1 Transitional Losses                                 | 30      |

| 2.1.2 Gate & Switching Node Capacitance Losses Estimation | 35      |

| 2.2 Conduction Losses Analysis                            | 43      |

| 2.2.1 Power FETs Conduction Losses Estimation             | 43      |

| 2.2.2 Parasitics Conduction Losses Estimation             | 44      |

| 2.2.3 Body-Diode Losses Estimation                        | 45      |

| 2.3 Simulation & Validation                               | 46      |

| 2.4 Conclusion                                            | 58      |

| 2.5 References                                            | 59      |

| CHAPTER 3. A FULLY-INTEGRATED BUCK REGULATOR WITH ON-     |         |

| CHIP PASSIVES AND CIRCUIT STUFFING                        | 60      |

| 3.1 Feasibility Analysis and Optimization                 | 61      |

| 3.2 Proposed Architecture                                 | 67      |

| 3.3 Circuit Implementation                                | 69      |

| 3.3.1 Power Train and Self-Regulation                     | 69      |

| 3.3.2 Compensator                                         | 70      |

| 3.3.3 PWM Comparator                                      | 71      |

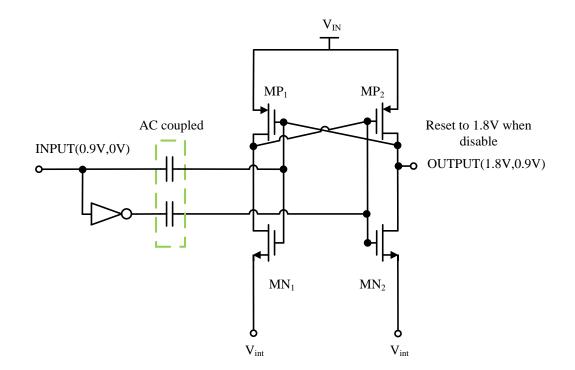

| 3.3.4 Dynamic Level Shifter                               | 73      |

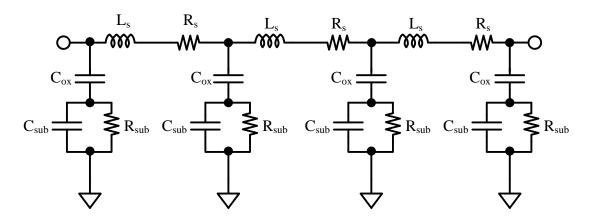

| 3.4 On-Chip Inductor Design and Modeling                  | 74      |

|                                                           |         |

Page

| 3.5 Experimental Results                                                                                                              | 79         |

|---------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.6 Conclusion                                                                                                                        | 81         |

| 3.7 References                                                                                                                        | 83         |

| CHAPTER 4. A DCM-ONLY BUCK REGULATOR WITH HYSTERETIC-<br>ASSISSTED ADAPTIVE MINIMUM On-TIME CONTROL<br>FOR LOW-POWER MICROCONTROLLERS | 85         |

| 4.1 Limitations of Existing Control Schemes in Handling a Wide                                                                        |            |

| Range of Operating Scenarios in DCM                                                                                                   | 87         |

| 4.2 Proposed Control Scheme                                                                                                           | 88         |

| 4.3 Power-Gating and Circuit Implementation                                                                                           | 98         |

| 4.3.1 Adaptive Minimum Constant On-time Pulse Generator                                                                               | 99         |

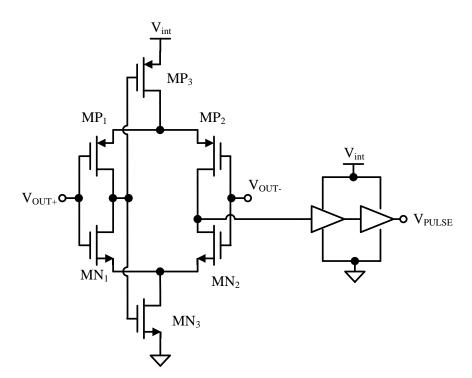

| 4.3.2 Control Comparator                                                                                                              | 101        |

| 4.4 Measurement Results                                                                                                               | 102        |

| 4.5 Conclusion                                                                                                                        | 111        |

| 4.6 References                                                                                                                        | 112        |

| CHAPTER 5. CONCLUSION                                                                                                                 | 115        |

| 5.1 Fully Integrated DC-DC Buck Converter in DCM/PFM Scenario 5.2 References                                                          | 116<br>119 |

| BIBLIOGRAPHY                                                                                                                          | 120        |

| ACKNOWLEDGEMENTS                                                                                                                      | 128        |

## LIST OF TABLES

| Table 2.1. Design parameters for CCM scenario.                                   | 49  |

|----------------------------------------------------------------------------------|-----|

| Table 2.2. Design parameters for DCM scenario.                                   | 49  |

| Table 3.1. Loss and passive components comparison between $0.35\mu m$ and $65nm$ |     |

| technologies                                                                     | 64  |

| Table 3.2. Design Parameter for On-Chip Inductor                                 | 77  |

| Table 4.1. Performance Summary                                                   | 103 |

| Table 4.2. Performance Comparison with other Published Work                      | 111 |

#### LIST OF FIGURES

v

|                                                                                       | Page |

|---------------------------------------------------------------------------------------|------|

| Figure 1.1. Schematic of a typical linear regulator with P type MOSFET as power       |      |

| transistor                                                                            | 5    |

| Figure 1.2. A block diagram of a typical DC-DC buck regulator topology                | 7    |

| Figure 1.3. Two-Step power conversion scheme for SoCs based on a separate PMIC an     |      |

| arrays of on-chip power converters within the SoC itself                              | 11   |

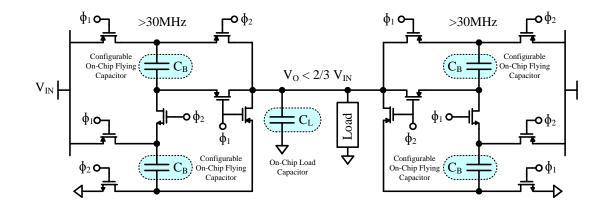

| Figure 1.4. Examples of on-chip power regulator topologies: Linear topology           | 13   |

| Figure 1.5. Examples of on-chip power regulator topologies: Capacitor-based topology  | 16   |

| Figure 1.6. Examples of on-chip power regulator topologies: Inductor-based topology   | 16   |

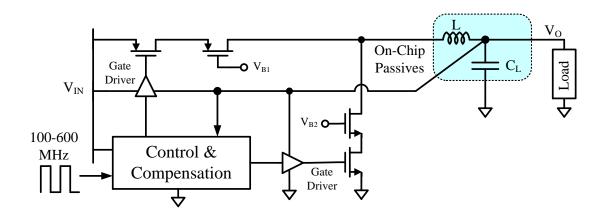

| Figure 1.7. A block diagram of a typical SIMO power converter topology                | 18   |

| Figure 2.1. (a) A typical buck converter including critical parasitics, and important |      |

| waveforms in (b) CCM operation, and (c) DCM operation                                 | 29   |

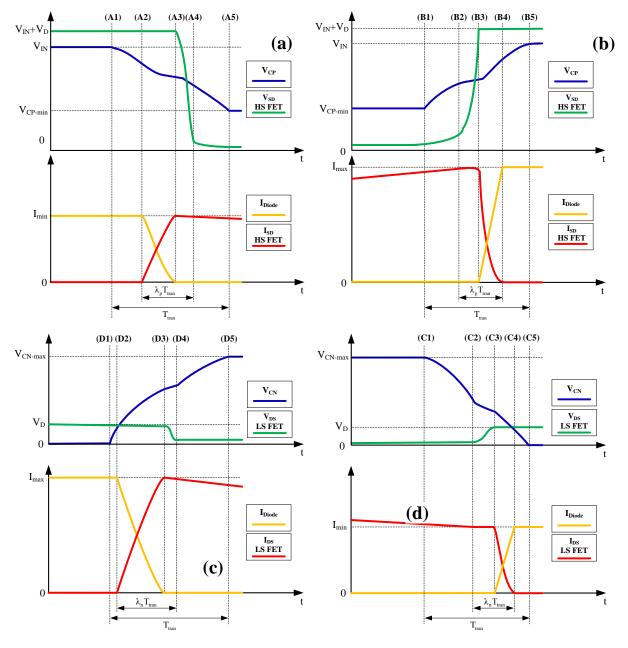

| Figure 2.2. A plot of the control signal of each power FET along with the voltage and | d    |

| current across the FET's drain-source terminals during the switching event            | S    |

| noted in Fig. 1.1: (a) high-side FET in event (A), (b) high-side FET in even          | ıt   |

| (B), (c) low-side FET in event (D), and (d) low-side FET in event (C)                 | 36   |

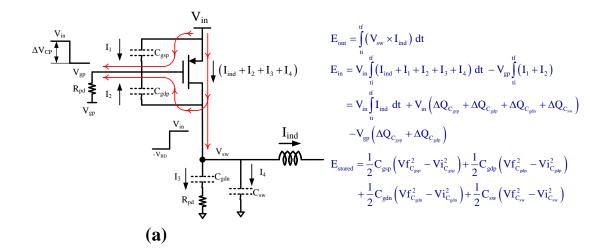

| Figure 2.3. Charge flow diagrams and loss equation derivations for CCM operation for  |      |

| (a) Event A (b) Event B                                                               | 41   |

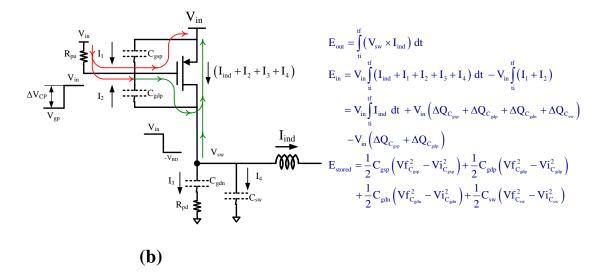

| Figure 2.4. Charge flow diagrams and loss equation derivations for CCM operation for  |      |

| (a) Event C (b) Event D                                                               | 42   |

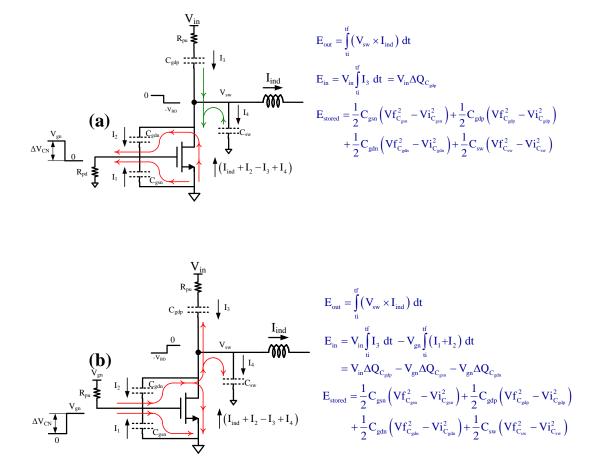

| Figure 2.5. Charge flow diagrams and loss equation derivations for DCM operation for  |      |

|                                                                                       |      |

(a) Event A (b) Event D

المنسارات

43

52

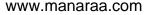

- Figure 2.6. The comparison between calculated and simulated power conversion efficiency in CCM and DCM scenarios with rail-to-rail gate control(a) CCM(b) DCM

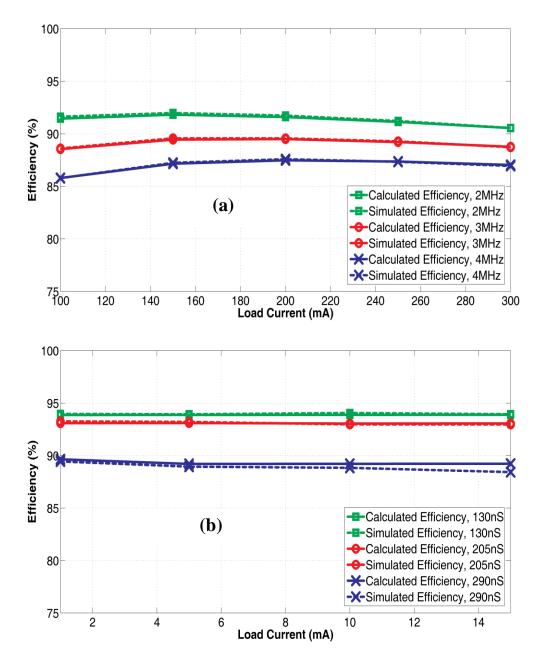

- Figure 2.7. The comparison between calculated and simulated power conversion efficiency in CCM and DCM scenarios with non-rail gate control(a) CCM (b) DCM 53

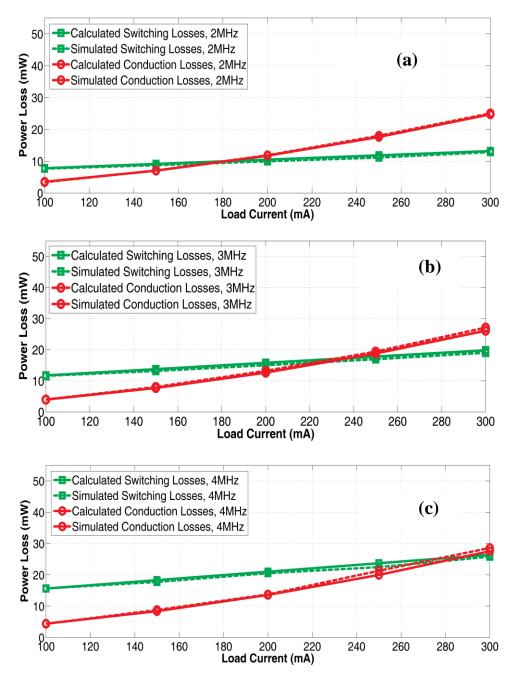

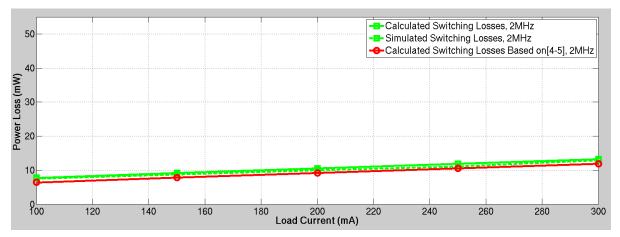

- Figure 2.8. The comparison between calculated and simulated switching & conduction losses in CCM scenarios with rail-to-rail gate control: (a) CCM with 2MHz switching frequency (b) CCM with 3MHz switching frequency (c) CCM with 4MHz switching frequency

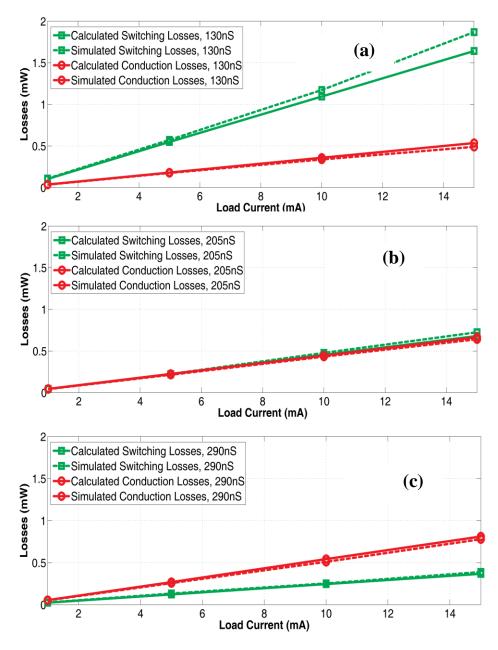

- Figure 2.9. The comparison between calculated and simulated switching & conduction losses in DCM scenarios with rail-to-rail gate control: (a) DCM with 130nS

Ton (b) DCM with 205nS Ton (c) DCM with 290nS Ton 55

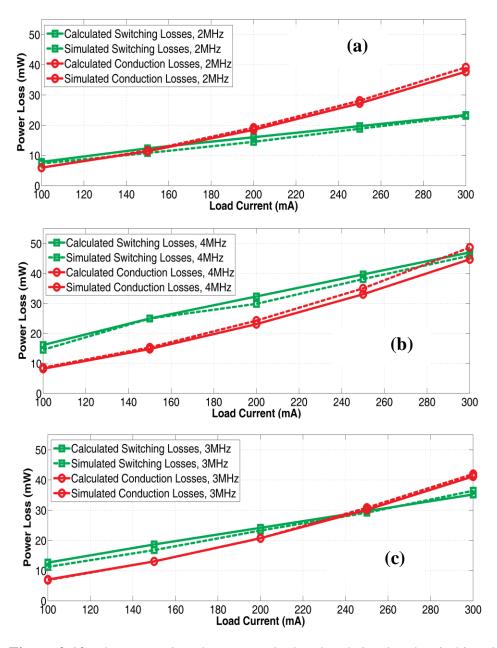

- Figure 2.10. The comparison between calculated and simulated switching & conduction losses in CCM scenarios with non-rail gate control: (a) CCM with 2MHz switching frequency (b) CCM with 3MHz switching frequency (c) CCM with 4MHz switching frequency

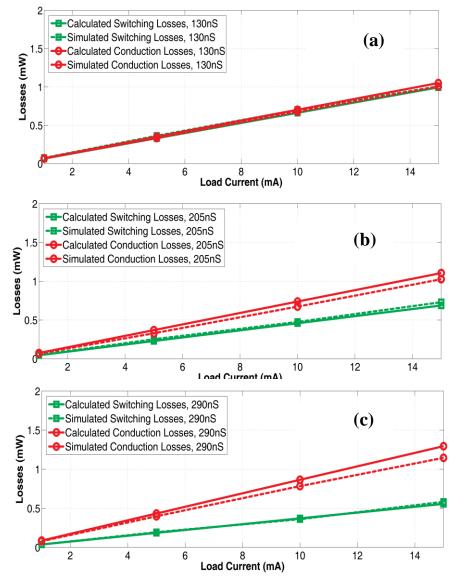

- Figure 2.11.The comparison between calculated and simulated switching & conduction losses in DCM scenarios with non-rail gate control: (a) DCM with 130nS

Ton (b) DCM with 205nS Ton (c) DCM with 290nS Ton 57

- Figure 2.12. The comparison between calculated switching losses with proposed formulas in this thesis, calculated switching losses with formulas proposed in[4-5], simulated switching losses in CCM scenarios at 2MHz switching frequency 58

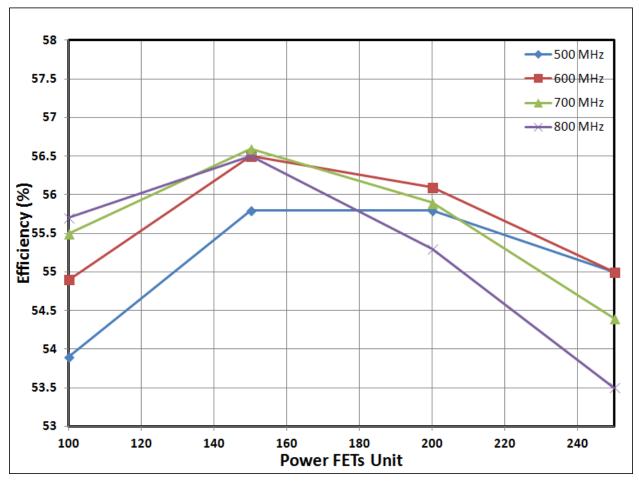

| Figure 3.1. The calculated efficiency of the regulator with different power FETs size       |    |

|---------------------------------------------------------------------------------------------|----|

| under different switching frequency                                                         | 66 |

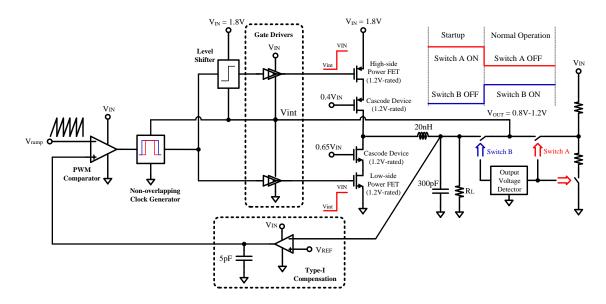

| Figure 3.2. Top level block diagram for proposed buck regulator showing the self-           |    |

| regulation scheme, loop compensation, and the cascoded power switches                       | 68 |

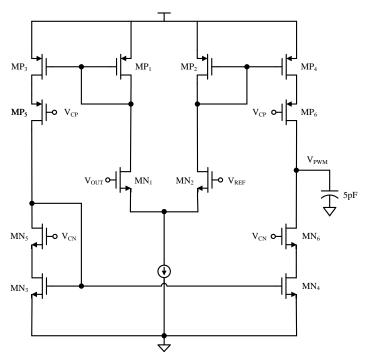

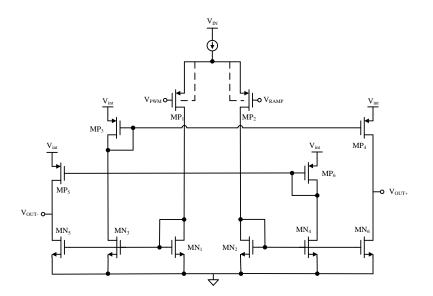

| Figure 3.3. Schematic of the proposed compensator of the fully-integrated buck regulator    | 72 |

| Figure 3.4. Schematic of the proposed PWM comparator of the fully-integrated buck           |    |

| regulator                                                                                   | 72 |

| Figure 3.5. Schematic of the proposed buffer stage of the PWM comparator                    | 73 |

| Figure 3.6. The schematic of the proposed dynamic level shifter                             | 74 |

| Figure 3.7. Three-segment lumped circuit model of the on-chip inductor                      | 76 |

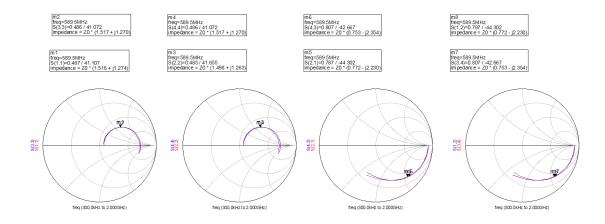

| Figure 3.8. Proposed Inductor S-Parameter Simulation Results: Red Curve Inductor, Blue      |    |

| Curve ideal elements                                                                        | 77 |

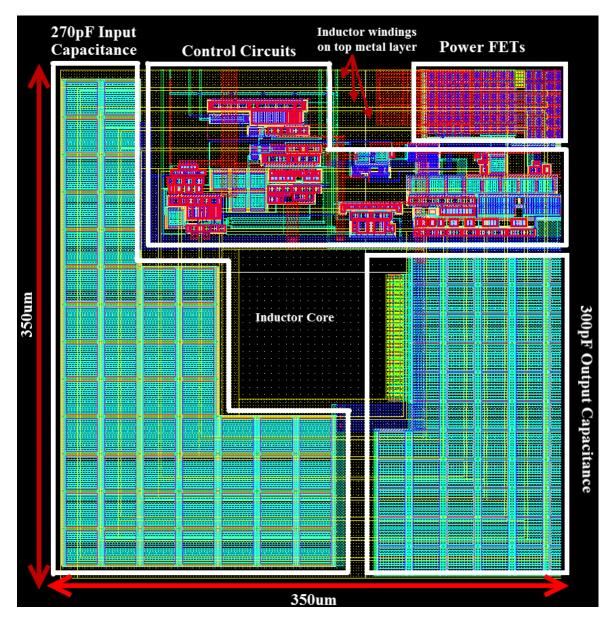

| Figure 3.9. The layout of proposed buck regulator with circuit stuffing                     | 78 |

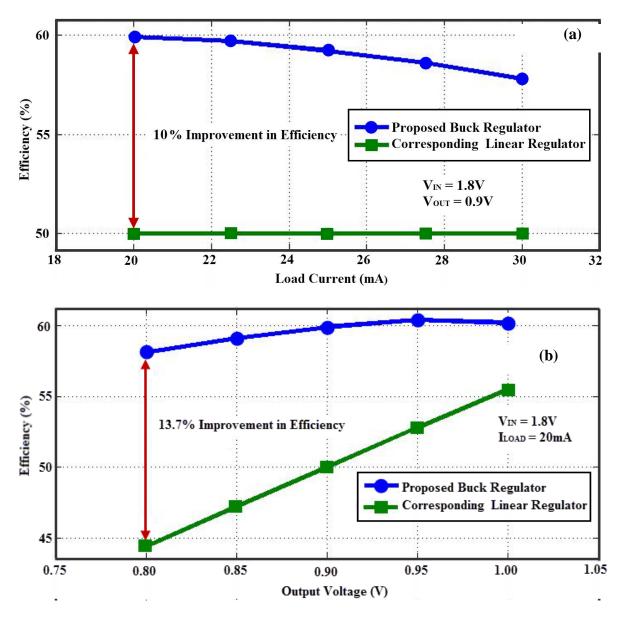

| Figure 3.10. The simulated efficiency of the extracted layout of the proposed regulator: a) |    |

| versus load current, and b) versus output voltage                                           | 80 |

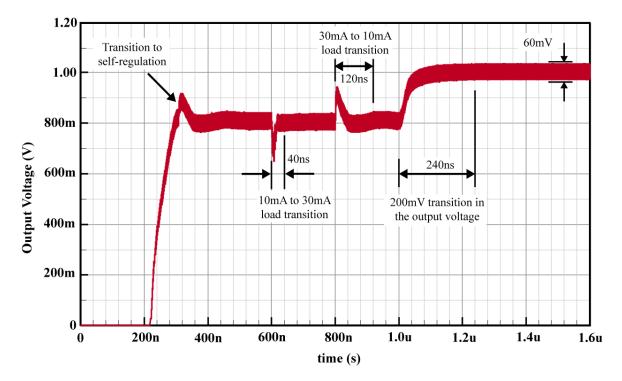

| Figure 3.11. Transient response of the extracted layout of the proposed regulator showing   |    |

| response to load/output voltage steps and self-regulation transition                        | 81 |

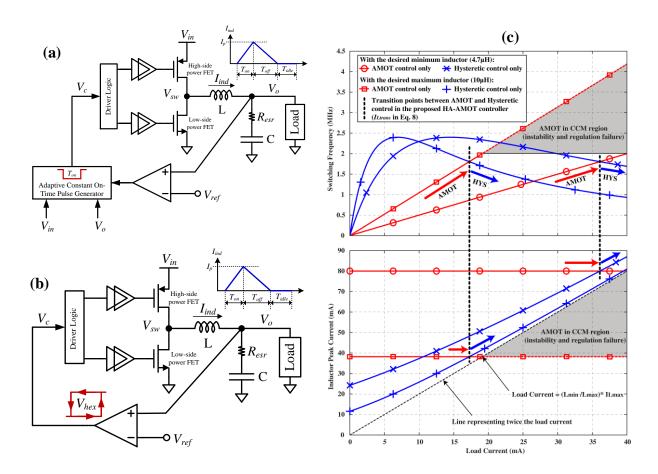

| Figure 4.1. Conventional controllers operating in DCM: (a) ACOT, and (b) Voltage-           |    |

| mode hysteretic. (c) Simulated inductor peak current and switching                          |    |

| frequency versus load for the AMOT controller alone, hysteretic controller                  |    |

| alone, and the transition between them in the proposed Hysteretic-Assisted                  |    |

| AMOT controller                                                                             | 90 |

vii

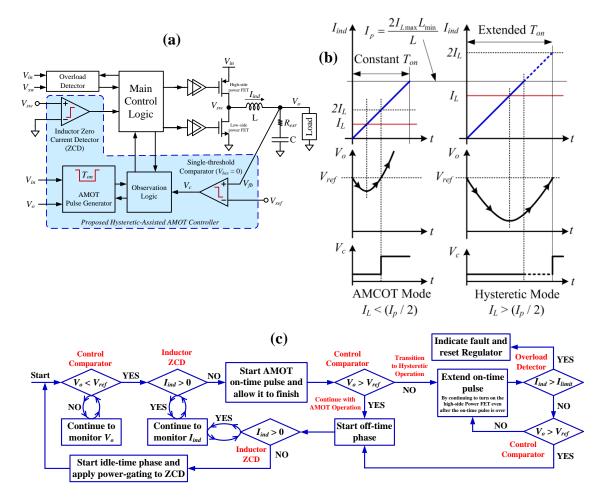

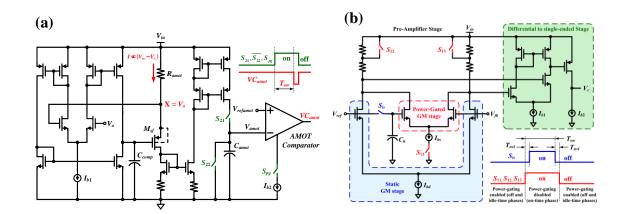

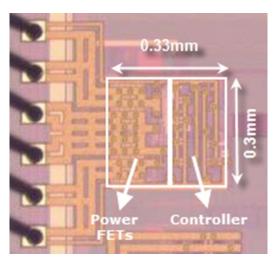

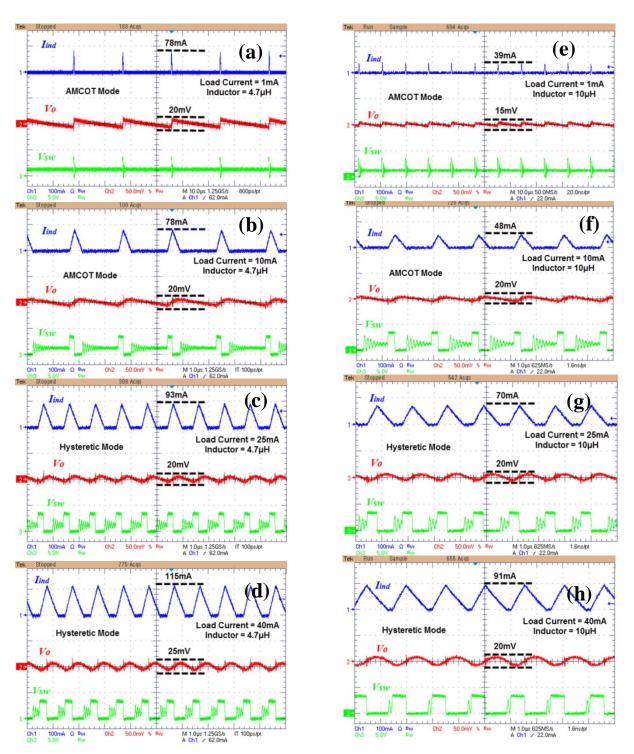

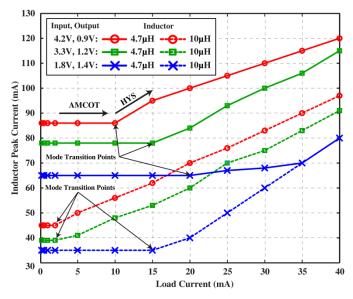

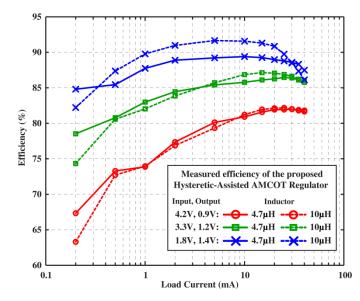

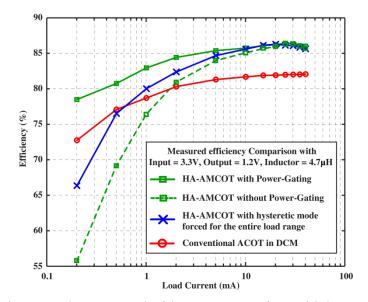

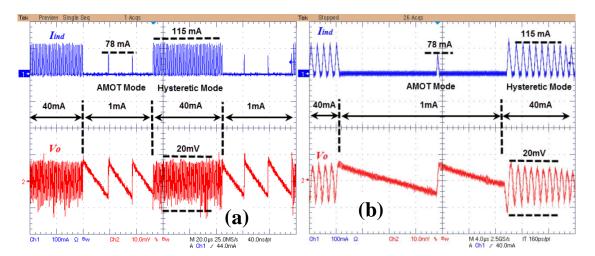

Figure 4.2. (a) Block diagram of the proposed HA-AMCOT controller, (b) Important signals showing the operation of the controller when the load current is less than, or higher than half the constant inductor peak current, and (c) A complete flow chart descriping the operation. 96 Figure 4.3. Schematics of the proposed: (a) AMOT pulse generator with power-gating, and (b) Control comparator with power-gating. 98 Figure 4.4. Die photo of the proposed HA-AMOT regulator showing double bonding at the 103 input ground rails, as well as the switching node. Figure 4.5. Transient measurements showing inductor current, output voltage, and switching node of the proposed regulator with 3.3V input voltage, 1.2V output voltage, and various load currents. (a), (b), (c), and (d) show the results with a 4.7 $\mu$ H inductor, while (e), (f), (g), and (h) show the results with a 10 $\mu$ H 106 inductor Figure 4.6. Measured inductor peak current versus load for various scenarios showing the 107 transition points between the AMOT and hysteretic modes. Figure 4.7. The measured efficiency versus load current of the proposed HA-AMOT regulator for various operating scenarios 107 Figure 4.8. Comparison between the measured efficiency using the HA-AMOT control with and without power-gating, with hysteretic mode forced across the entire

load range (pure hysteretic operation), and with the on-time modified to operate

as a conventional ACOT controller in DCM.

المنسارة للاستشارات

108

Figure 4.9. The regulator's response to a 1mA to 40mA load step with 3.3V input, 1.2V output, and 4.7µH inductor: (a) with a 20µs time scale, and (b) with a 4µs time scale and more frequent load 108

#### ABSTRACT

As System-on-Chip (SoCs) in nanometer CMOS technologies grow larger, the power management process within these SoCs becomes very challenging. In the heart of this process lies the challenge of implementing energy-efficient and cost-effective DC-DC power converters. To address this challenge, this thesis studies in details three different aspects of DC-DC power converters and proposes potential solutions. First, to maximize power conversion efficiency, loss mechanisms must be studied and quantified. For that purpose, we provide comprehensive analysis and modeling of the various switching and conduction losses in low-power synchronous DC-DC buck converters in both Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM) operation, including the case with nonrail gate control of the power switches. Second, a DC-DC buck converter design with only on-chip passives is proposed and implemented in 65-nm CMOS technology. The converter switches at 588 MHz and uses a 20-nH and 300-pF on-chip inductor and capacitor respectively, and provides up to 30-mA of load at an output voltage in the range of 0.8-1.2V. The proposed design features over 10% improvement in power conversion efficiency over a corresponding linear regulator while preserving low-cost implementation. Finally, a 40-mA buck converter design operating in the inherently-stable DCM mode for the entire load range is presented. It employs a Pulse Frequency Modulation (PFM) scheme using a Hysteretic-Assisted Adaptive Minimum On-Time (HA-AMOT) controller to automatically adapt to a wide range of operating scenarios while minimizing inductor peak current. As a result, compact silicon area, low quiescent current, high efficiency, and robust performance across all conditions can be achieved without any calibration.

#### CHAPTER I. INTRODUCTION

The wide use of portable communication, navigation, and multi-media devices has fueled the demand for increasing the functional capabilities of these devices while reducing their power consumption and implementation size and cost. To meet this demand, the concept of mixed-signal System-on-Chip (SoC) has been introduced, where numerous analog, RF, and digital processing circuitries are implemented together in a single CMOS chip [1, 2]. The SoC concept, along with the dramatic scaling of the feature size of CMOS technologies to the nanometer levels, have been certainly transformational in terms of expanding the functional capabilities of mobile devices and reducing their power, size, and cost. Nonetheless, several complex challenges in terms of how power can be delivered to the SoC have been introduced as a byproduct of the SoC concept itself as well as the nature of nanometer CMOS technologies. Firstly, the SoC concept entails that the SoC contains an extensive mix of various circuit functions (analog, RF, and digital), with each function requiring its own independent and isolated power supply domain with unique specifications. Even within a specific circuit function, several independent power supply domains may be required. For instance, a data converter function may require a power supply domain for its analog part and another one for its digital part. As a result, the number of independent power supply domains in SoCs has grown significantly, and can easily exceed 30 in larger SoCs [2]. Implementing such a large number of power supply domains is very challenging in terms of cost and size. This is due to the fact that traditional power supplies require energy-storing passive components (i.e. inductors and capacitors) that are too large to integrate on chip, and therefore must be off chip. In addition to the fact that these off-chip passive components are

relatively expensive, they also consume significant real state area on the Printed Circuit Board (PCB), which further increases the cost and size of the system. Moreover, for the SoC to utilize these off-chip passive components, additional package pins become necessary, which is difficult to accommodate in pin-limited SoCs without adopting larger and more expensive packaging options. Secondly, as CMOS technology scales down to nanometer levels, the voltage rating of its devices, as well as the power supply levels required by the various circuit functions within the SoC, scale down to 1.8V or lower. Utilizing these devices to implement power supplies that operate from a Li-Ion battery with voltage levels as high as 5V while ensuring the reliability of these devices becomes challenging, and often times comes at the expense of complicated design and large silicon area [3], or additional mask cost for implementing special high-voltage devices [4, 5].

In this chapter, we will first introduce the basics of power conversion schemes, focusing on the step-down converting solutions. The introduction includes the definitions and basic components that are widely implemented across may applications. After that, the different methods that can be employed to generate a large number of power supply domains from a single shared battery in mixed-signal SoCs are discussed, along with the advantages and limitations of each method in terms of efficiency, dynamic operation, and cost. This includes two-step approaches that involve a separate Power Management Integrated Circuit (PMIC) for primary power conversion, followed by secondary power converters within the SoC itself to generate multiple on-chip power supply domains. These secondary power converters can be linear regulators, or alternatively, can be fully-integrated high-frequency switched-C and switched-L regulators with on-chip passive components in order to improve power conversion efficiency. Single-step approaches will also be discussed, which includes

Single-Inductor-Multiple-Output (SIMO) power conversion schemes. This chapter will also give an overview of some proposed techniques that can be used to reduce the silicon area overhead of on-chip power supplies, along with techniques to improve the power conversion efficiency as well as dynamic and noise performance. Finally, the organization of the thesis will be discussed.

#### 1.1 Basics on Power Conversion Schemes

As it is discussed previously, nanometer CMOS mixed-signal SoCs requires a large number of independent and well-isolated power domains with only limited input power sources. Most likely, the power source will be a single battery with higher voltage than the desired voltage level for the system(e.g. coin cell battery or Li-Ion battery). Thus, step-down power converters are widely implemented in order to generate these power domains from a single power source. In general, there are two categories of broadly used DC-DC step-down converters: (a) linear regulators; (b) switching regulators.

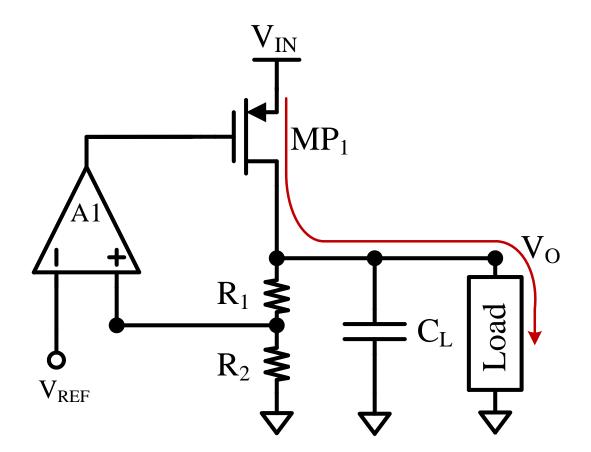

Fig. 1.1 shows the schematic of a generic linear regulator with a P type  $MOSFET(MP_1)$  as the power transistor. By adjusting the resistive divider  $R_1$  and  $R_2$ , the regulator is able to maintain a constant output voltage as:

$$V_{O} = V_{REF} \times \frac{R_{1} + R_{2}}{R_{2}}$$

(1.1)

where  $V_{REF}$  typically comes from the band-gap. Depending on the application and the type of the load, the output capacitor  $C_L$  can be implemented either on PCB or integrated on die[6, 7]. The way this circuit works is that the feedback loop constantly modulating the resistance of the power transistor  $MP_1$  so as to create a resistive ladder between  $MP_1$  and the load, creating the regulated output voltage  $V_0$  while dumping current that is consumed by the load. In general, the feedback loop architecture may vary while the power transistor may also be implemented as a N type MOSFET depending on the application and the compensation techniques[8]. The advantage of this type of regulator is simple to implement, robust and low cost.

One major disadvantage of the linear regulator is that the power conversion efficiency degrades with respect to the ratio between the input and the output of the regulator since all the current delivering to the load also flows through  $MP_1$ . Thus, the power conversion efficiency of the linear regulator can be approximately derived as:

$$\eta = \frac{P_0}{P_{IN}} = \frac{V_0 \times I_0}{V_{IN} \times I_{IN}} \tag{1.2}$$

While  $P_0$  and  $P_{IN}$  are denoted as output and input power, respectively. Note that the input power calculation ignores the power consumed by amplifier  $A_1$  assuming it is relatively small(e.g. tens of  $\mu$ A). Based on eq. (1.2), the power conversion efficiency with input voltage as 3.3 V and output voltage as 1.2 V can only be approximately 36%, which is considered as fairly inefficient. DC-DC switching regulators, on the other hand, are famous for their high power conversion efficiency over a wide range of input and output conditions. This has been realized by transferring energy between energy-storage elements(e.g. inductor and capacitor) based on certain patterns(e.g. turn on and off switches)[9-10]. By doing this, the energy is

saved since the power switches do not have to constantly burning all the redundant power any more comparing to the linear regulator since the energy can be stored on those energystorage components. Among all types of DC-DC step-down switching regulators, the inductor based, DC-DC buck regulator is the best in class in terms of the power conversion

**Figure 1.1.** Schematic of a typical linear regulator with P type MOSFET as power transistor

efficiency. Based on the report from the literatures, those kind of switching regulator can achieve 95% efficiency and above[11].

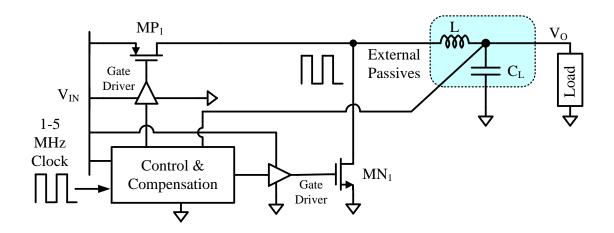

The block diagram of a typical DC-DC buck regulator is shown in Fig. 1.2. This type of regulator is typically composed with an off-chip inductor and an off-chip capacitor at 1-100  $\mu$ H and  $\mu$ F level. The high-side power transistor  $MP_1$  and low-side power transistor  $MN_1$  and their corresponding gate driver are the major contributor to the total silicon area. This will help reduce the conductional loss due to charging and discharging the inductor in order to achieve high power conversion efficiency. The control and compensation block is typically composed of amplifiers, comparators, ramp generators and digital logic circuits, etc. The functionality of this block is to properly control the on/off of the high-side power transistor  $MP_1$  and low-side power transistor  $MN_1$  so that a desired output level can be generated and maintained. Note that the output level is a DC voltage with AC component on top of it. This AC component is called "ripple" and typically stays in the range of a few mV to tens of mV.

Typically, the "on" time of the high-side power transistor  $MP_1$  is defined as  $T_{on}$  while the "on" time of the low-side power transistor  $MN_1$  is defined as  $T_{off}$ . To control the buck regulator, one famous control topology, Pulse-Width-Modulation(PWM) control is to keep the sum of  $T_{on}$  and  $T_{off}$  unchanged(e.g. fixed switching frequency) while modulating the ratio between  $T_{on}$  and  $T_{off}$  to achieve the desired output voltage level. On the other hand, one can also keep  $T_{on}$  or  $T_{off}$  unchanged and modulating the operating frequency of the regulator to achieve the same goal. This type of control topology is referred as Pulse-Frequency-Modulation(PFM) control. No matter which control topology is used, as long as the regulator stays in Continuous-Conduction-Mode(CCM) condition, the relationship between the input and output can be derived as[12]:

$$V_0 = V_{IN} \times \frac{T_{on}}{T_{on} + T_{off}}$$

(1.3)

By analyzing the above equation, one can easily come to the conclusion that, in theory, the regulator can generate the same output voltage with different switching frequency as long as the ratio between the high-side power transistor "on" time and total period is the same. However, this does not mean that designer can pick whatever switching frequency they want in the actual design. In general, the operating frequency of the regulator is inversely proportional to the ripple at the output. On the other hand, the power loss due to turning on/off the power transistors is proportional to the operating frequency. Thus, designers need to carefully budget all the design parameters so as to achieve the best performance of the regulator based on the specific application.

Figure 1.2. A block diagram of a typical DC-DC buck regulator topology

The efficiency analysis for a buck regulator is slightly different than the linear regulator since the loss mechanism of a buck regulator is more complex. In general, there are two types of losses in a buck regulator: a) conductional losses; b) switching losses. Conductional losses are due to the finite resistance of the power transistor  $MP_1$  and  $MN_1$  while the switching losses are due to the energy it takes to charge and discharge the parasitic capacitance of the power transistor(e.g. gate to source capacitance). Thus, the efficiency of a buck regulator can be derived as:

$$\eta = \frac{P_0}{P_{IN}} = \frac{P_0}{P_0 + P_{loss\_cond} + P_{loss\_sw}}$$

(1.4)

Where  $P_{loss\_cond}$  and  $P_{loss\_sw}$  represent the conductional losses and switching losses, respectively. In general, for a given input and output condition,  $P_{loss\_cond}$  is proportional to the product of the load and the "on" resistance of the power transistor while  $P_{loss\_sw}$  is proportional to the product of the equivalent gate capacitance of the power transistor and the switching frequency. Moreover, the "on" resistance of the power transistor is inversely proportional to the total gate capacitance of the power transistor since a "larger" MOSFET typically contains more parasitic capacitance. Thus, for a given load and switching frequency, it is possible to arrive at an optimized size of the power transistor after some iteration.

Typically, the PWM control topology is widely used for the load range around hundreds of mA as it can achieve a relatively flat and optimum efficiency curve over a wide range of load variation[13]. However, once it comes to light load conditions(e.g. less than 10mA), the switching losses will dominate the conduction losses, causing a massive

efficiency degradation. In this case, the PFM control is preferred since the switching frequency can be adjusted depending on the load conditions so that the switching losses and conduction losses can be balanced. Thus, the classic DC-DC buck regulator typically contains both PWM and PFM modes so as to achieve high efficiency curve over a wide load range(e.g. 10mA to 1A)[14].

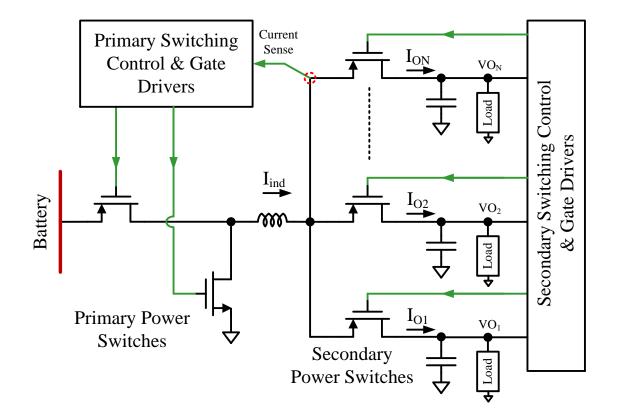

#### 1.2 Two-step Power Conversion Schemes

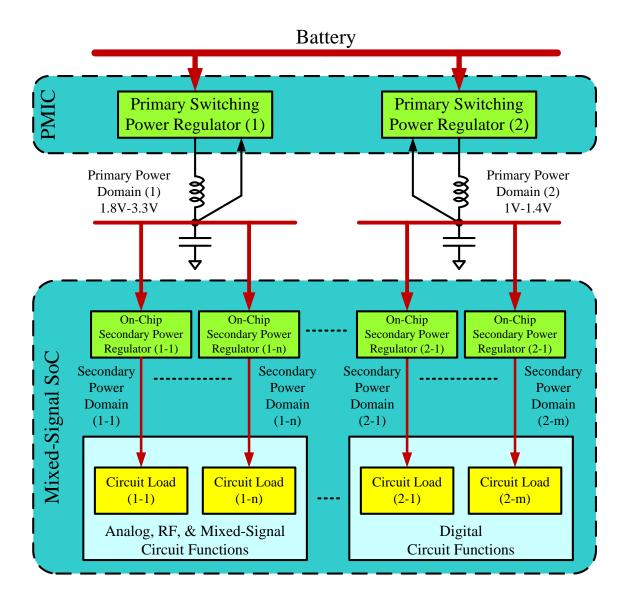

Conceptually, all the power supply domains needed by the SoC can be implemented externally with high power conversion efficiency using a separate Power Management Integrated Circuit (PMIC) and then delivered to the SoC. However, as the number of power supply domains increases, this solution becomes unrealistic from a cost and size perspective, not only due to the passive components involved, but also due to the large count of package pins that would be required in the PMIC and the SoC to connect these power supply lines. Moreover, since the SoC may require many of these power supplies to be adaptive (i.e. their voltage levels may need to be varied with time to optimize the load performance), some form of communication between the SoC and the PMIC is necessary, which adds to the complexity of the system design and limits the speed at which these power supplies can be adapted by the SoC. Moreover, due to the package and PCB parasitics associated with routing these power supply lines, the overall efficiency and the dynamic performance of the power supplies can be significantly degraded. For the above reasons, the two-step approach shown in Fig. 1.3 has become the most attractive and commonly-employed power conversion scheme in SoCs today. As shown, a separate PMIC is still used, but only for generating a

limited number of primary power supply domains directly from the battery, typically one for analog functions and another for digital functions [1, 2]. These shared power supplies are usually implemented using switching power regulators, and thus offer high power conversion efficiency. Subsequently, these primary power supplies are used to generate a large number of independent secondary power supplies within the SoC itself using arrays of on-chip power regulators. This two-step approach has the advantage of limiting the number of external power supplies that must be routed to the SoC, which saves a significant count of package pins. Furthermore, the separate PMIC can be implemented in a suitable CMOS technology that can interface with the high-voltage battery without reliability concerns. Moreover, since the primary power supplies routed to the SoC have much lower voltage levels, implementing the secondary on-chip power supplies within the SoC using nanometer CMOS technology is greatly simplified in terms of reliability. Additionally, with the secondary power supplies integrated within the SoC, adapting them dynamically to the specific demand of their loads can be done without the complexity of communicating with the PMIC. Finally, the off-chip passive components count is greatly reduced as they are needed for only few primary power supplies, which reduces the size and cost of the whole system. The on-chip secondary power supplies can be implemented in several ways as detailed below.

www.manaraa.com

**Figure 1.3.** Two-Step power conversion scheme for SoCs based on a separate PMIC and arrays of on-chip power converters within the SoC itself.

#### **1.2.1 Fully-Integrated Linear Regulators**

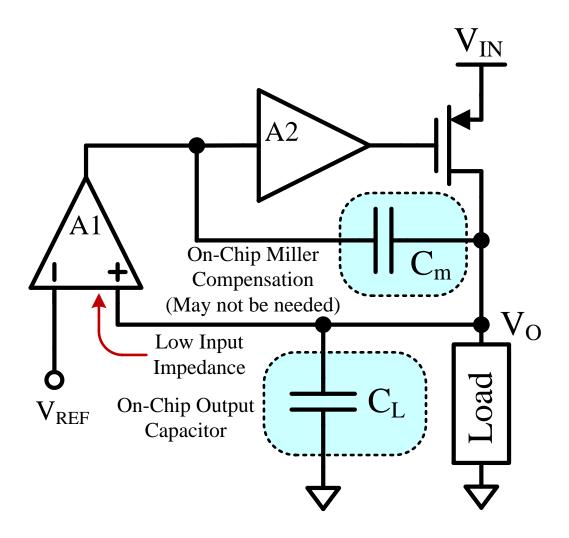

Linear regulators are very popular due to their relatively compact size and small passive components count (usually a single capacitor), which help reducing their implementation cost. Moreover, they offer low noise performance due to lack of inherent

switching, as well as their ability to suppress noise from the primary power supplies. Although conventional linear regulators require output capacitors that are too large to integrate on chip, numerous new topologies, example of which is shown in Fig. 1.4, have been proposed that enable their implementation using only hundreds of Pico-Farads capacitors [15-20]. These topologies have made linear regulators very popular in SoCs since fully-integrated realizations became possible with only on-chip capacitors. Moreover, many of these topologies offer wide-band performance when implemented in nanometer CMOS, which allows for faster dynamic operation. However, linear regulators suffer from poor power conversion efficiency and can significantly affect the overall efficiency of the system if widely used across the SoC. Moreover, fully-integrated topologies with on-chip capacitors suffer from poor Power Supply Rejection (PSR) around the typical frequencies used in the primary switching power lines and may require employing complicated control techniques in the primary power supplies to reduce their switching noise [21-23].

Figure 1.4. Examples of on-chip power regulator topologies: Linear topology

#### **1.2.2 Fully-Integrated Switching Regulators**

To circumvent the efficiency degradation caused by employing linear regulators as secondary power supplies within SoCs, they can be replaced by fully-integrated capacitor-

based [2, 24-27] or inductor-based [28-31] switching regulators, examples of which are shown in Fig. 1.5 and 1.6. Traditionally, these regulators require large off-chip passive components due to their low switching frequency, which can't be increased to avoid excessive switching losses and degraded efficiency. However, with the scaling of CMOS technologies to nanometer levels, these regulators can be implemented with much higher switching frequencies while maintaining reasonable switching losses and better overall efficiency than linear regulators [1]. Consequently, the passive components required can be scaled down to levels where they can be implemented on-chip [2, 24-31], and much faster dynamic performance can be achieved.

One major limitation of fully-integrated realizations of switching regulators, however, is their large silicon area compared to linear regulators, primarily due to the area overhead of the on-chip passives. In fact, the area of some of these realizations can consume between twice to ten times the area of a corresponding linear regulator. In inductor-based realizations, this problem is exacerbated by the fact that the area underneath on-chip inductors (implemented using top thick metal layers) is left unused to avoid additional losses through electromagnetic coupling with any circuits or routing underneath the inductor. This forces implementing the rest of the regulator's circuitry (including the output capacitor) outside the inductor area, leading to much larger silicon area. To reduce the overall area, there have been recent proposals to stuff circuits underneath on-chip inductors, particularly in step-down regulators [30]. These implementations rely on the fact that the switching frequency, though high, but not as high as RF applications where electromagnetic coupling losses are a real concern. Moreover, since in step-down regulators the output capacitor is shorted to one side of the inductor anyway, it may be feasible to at least stuff that capacitor underneath the

inductor. These realizations can significantly reduce the total area of the regulator to bring it closer to the area of a corresponding linear regulator. In capacitor-based realizations, there is little that can be done, other than increasing the switching frequency, to reduce the total area because the on-chip capacitors use the poly-well layers, which renders their area unusable for anything else.

Another major limitation of fully-integrated realizations of switching regulators is the quality factor of the on-chip passive components, which significantly degrades the overall power conversion efficiency. In inductor-based realizations, the series resistance of the onchip inductor dominates the losses and limits the overall efficiency to about 10% better than linear regulators in best case scenarios [30]. This can be circumvented in some cases by using multi-phase designs to reduce conduction losses in the inductor and use non-standard CMOS technologies that offer additional thick metal layers for implementing higher quality inductors [29, 31]. However, these technologies are more expensive than standard CMOS and are difficult to justify in commercial applications that do not contain RF functions. There have also been proposals to employ on-package air-inductors [32] or bond-wire inductors [33] that feature better quality than on-chip counterparts. However, this requires special packaging consideration, and thus cost, pin count, and integration continues to be a challenge. On the other hand, the bottom plate parasitics of on-chip capacitors limit the overall efficiency of capacitor-based realizations of fully-integrated switching regulators [2]. Nevertheless, recently reported implementations are showing a great promise for achieving higher levels of efficiency than inductor-based counterparts [24].

Figure 1.5. Examples of on-chip power regulator topologies: Capacitor-based topology [2]

Figure 1.6. Examples of on-chip power regulator topologies: Inductor-based topology [30].

#### 1.3 One-step Power Conversion Schemes

A major limitation of the two-step power conversion approach discussed in the previous section is the degraded efficiency resulting from cascading power converters. For instance, cascading two power converters, each with 80% efficiency, results in an overall efficiency of only 64%. For that reason, single-step switching power conversion schemes that

operate directly from the battery and implemented within the SoC are becoming increasingly popular. In addition to the efficiency advantage of this strategy, it also eliminates the need for a separate PMIC. To avoid the large count of passive components, particularly inductors, SIMO topologies such as the one shown in Fig. 1.7 have been used to implement a large number of efficient power supplies for SoCs in nanometer CMOS technologies [34]. However, due to the high-voltage rating of Li-Ion batteries, special high-voltage transistors must be available in the technology flow to interface with the battery. This constitutes an additional cost beyond standard nanometer CMOS technology nodes. Moreover, although traditional SIMO topologies limit the number of inductors to only one, each power supply continues to require a large off-chip capacitor. This entails the same issues associated with the cost and size of these capacitors as well as the package pins count to interface with them as described in the previous section. Therefore, these topologies still create a tradeoff between cost and efficiency. Furthermore, since traditional SIMO topologies use low switching frequencies to achieve high efficiency, and since they must distribute the energy of a single inductor to many outputs in a sequential manner, their transient performance is typically slow, which limits the ability to dynamically adapt them as the SoC demands. The above limitations are spurring new research that attempts to reduce the output capacitors in single-step SIMO topologies to levels where they can be integrated on chip while preserving their efficiency advantage. This includes dual-frequency SIMO topologies that feature fullyintegrated outputs and offer very fast dynamic operation [35]. These topologies can enable the implementation of a large number of highly-efficient power supplies within the SoC without the overhead of off-chip capacitors.

Figure 1.7. A block diagram of a typical SIMO power converter topology

#### 1.4 Thesis Organization

The thesis is organized as follow:

Chapter 2 focuses on the theory of loss analysis of buck converter for low power nanometer CMOS applications. This chapter provides comprehensive analysis and modeling of switching and conduction losses in low-power synchronous buck regulators in both CCM and DCM modes of operation including the case with non-rail gate control of the power

FETs. The analysis takes into account losses that are typically ignored but become critical in low-power operation. It also considers the actual behavior of the regulator in DCM for loss modeling instead of common CCM-based approximations, which leads to more accurate estimation of losses. The provided comprehensive loss formulas can be used by designers to correctly optimize critical parameters in low-power buck regulators, such as the switching frequencies, sizes of the power FETs, realistic budgets for the parasitics associated with the passive components as well as the package so as to achieve the best possible efficiency. The theoretical formulas are verified against an actual buck regulator design implemented in 90nm CMOS technology.

Chapter 3 discusses a fully-integrated buck regulator with on-chip passives in 65nm standard CMOS technology is presented [36]. The proposed regulator switches at 588MHz and uses a 20nH on-chip inductor and a 300pF on-chip output capacitor. It operates from 1.8V input and produces an output in the range between 0.8V to 1.2V with maximum load current of 30mA. In order to reduce the large silicon area overhead of the on-chip inductor, the proposed design employs circuit stuffing where the entire regulator's circuitry is implemented directly underneath the inductor. This includes the input and output capacitance, power train, and control circuits. Thus, the total area of the regulator becomes essentially the area of the on-chip inductor itself, which cuts the regulator's footprint by 50%. Moreover, the proposed regulator employs a self-regulation loop that improves its overall efficiency and ensures the reliability of its low-voltage power transistors while operating from a 1.8V input. The regulator occupies 0.12mm<sup>2</sup> with a peak efficiency of 60%, and achieves up to 13.7% better efficiency than a corresponding LDO. It achieves fast settling

time of 240ns for a 200mV output voltage step, and as short as 40ns for a 20mA load current step.

Chapter 4 presents a 40mA buck regulator operating in the inherently stable Discontinuous Conduction Mode (DCM) for the entire load range is presented [37]. A Pulse Frequency Modulation (PFM) control scheme is implemented using a proposed Hysteretic-Assisted Adaptive Minimum On-Time (HA-AMOT) controller to automatically adapt the regulator to a wide range of operating scenarios in terms of input, output, and passive component values while ensuring compensation-less DCM operation with minimized inductor peak current. Thus, compact silicon area, low quiescent current, high efficiency, and robust performance across all possible scenarios can be achieved without any calibration. Moreover, power-gating is employed in the analog circuits of the proposed controller to further improve efficiency at sub-1mA loads. The regulator is integrated within a low-power microcontroller in 90nm CMOS to power its digital core while allowing maximum flexibility in the powering options of the microcontroller and the choice of the passive components. It occupies 0.1mm<sup>2</sup> and achieves 92% peak efficiency, and 78.5% and 86% efficiency at 200µA and 40mA loads respectively. It handles an input in the range of 1.8V-4.2V, an output in the range of 0.9V-1.4V, an inductor in the range of  $4.7\mu$ H-10 $\mu$ H, and an output capacitor in the range of  $2.2\mu$ F-10µF without any calibration or re-optimization. The whole thesis concludes in chapter 5 while some new ideas regarding fully integrated DC-DC buck converters are proposed.

#### 1.5 References

- [1] Wei Fu, and Ayman Fayed, "A Feasibility Study of High-Frequency Buck Regulators in Nanometer CMOS Technologies," *IEEE Dallas circuits and Systems Workshop* (DCAS 2009), pp. 31-34, Oct. 2009.

- [2] Y. K. Ramadass, A. A. Fayed, and A, P. Chandrakasan, "A fully integrated switchedcapacitor step-down DC-DC converter with digital capacitance modulation in 45 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2557-2565, Dec. 2010.

- [3] S. Bandyopadhyay, Y. K. Ramadass, and A, P. Chandrakasan, "20 μA to 100 mA DC– DC Converter With 2.8-4.2 V Battery Supply for Portable Applications in 45 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2807-2820, Dec. 2011.

- [4] E. Soenen et al., "A robust digital DC-DC converter with rail-to-rail output range in 40 nm CMOS," *IEEE International Solid-State Circuits Conference (ISSCC 2010)*, pp. 198–199, Feb. 2010.

- [5] F. Kuttner et al., "A Digitally Controlled DC-DC Converter for SoC in 28nm CMOS," *IEEE International Solid-State Circuits Conference (ISSCC 2011)*, pp. 384-385, Feb. 2011.

- [6] M. Al-Shyoukh, H. Lee and R. Perez, "A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator With Buffer Impedance Attenuation," *IEEE J. Solid-State Circuits*, vol. 42, no. 8, pp. 1732–1742, Aug. 2007.

- [7] X. Ming et al., "An Ultrafast Adaptively Biased Capacitorless LDO With Dynamic Charging Control," *IEEE Transactions on Circuits and Systems II*, vol. 59, no. 1, pp. 40-44, Jan. 2012.

- [8] T. Coulot et al., "Fully integrated power management unit (PMU) using NMOS Low Dropout regulators," *IEEE EUROCON 2013*, pp. 1445–1452, Jul. 2013.

- [9] Cheung Fai Lee and Philip K. T. Mok, "A Monolithic Current-Mode CMOS DC-DC Regulator with On-Chip Current-Sensing Technique," *IEEE Journal of Solid-State Circuits, vol. 39*, No. 1, January 2004.

- [10] Feng Su, Wing-Hung Ki, and Chi-Ying Tsui, "Regulated Switched-Capacitor Doubler With Interleaving Control for Continuous Output Regulation," *IEEE Journal of Solid-State Circuits*, vol. 44, No. 4, pp. 1112-1120, April 2009.

- [11] Patrick Y. Wu, Sam Y. S. Tsui, and Philip K. T. Mok, "Area- and Power-Efficient Monolithic Buck Regulators with Pseudo-Type III Compensation," *IEEE Journal of Solid-State Circuits*, vol. 45, No. 8, pp. 1446-1455, August 2010.

- [12] R. Erickson, and D. Maksimovic, "Fundamentals of Power Electronics," Kluwer Academic Publisher, Massachusetts, 2001.

- [13] A high efficiency monolithic synchronous step-down regular, data sheet, part # LTC1878, Linear Technology, http://cds.linear.com/docs/Datasheet/1878f.pdf.

- [14] Wan-Rone Liou, Mei-Ling Yeh, Yueh Lung Kuo, "A High Efficiency Dual-Mode Buck Regulator IC for Portable Applications," *IEEE Transactions on Power Electronics*, vol. 23, No. 2, pp. 667-677, March 2008.

- [15] P. Y. Or and K. N. Leung, "An output-capacitorless low-dropout regulator with direct voltage-spike detection," *IEEE J. Solid-State Circuits*, vol. 45, no. 2, pp. 458–466, Feb. 2010.

- [16] J. Guo, and K. N. Leung, "A 6-µW Chip-Area-Efficient Output-Capacitor-less LDO in 90-nm CMOS Technology," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1896-1905, Sept. 2010.

- [17] R.J. Milliken, J. Silva-Martinez, E. Sanchez-Sinencio, "Full On-Chip CMOS Low-Dropout Voltage Regulator," *IEEE Transactions on Circuits and Systems I*, vol. 54, no. 9, pp. 1879-1890, Sept. 2007.

- [18] W. Kruiskamp, R. Beumer, "Low drop-out voltage regulator with full on-chip capacitance for slot-based operation," *IEEE European Solid-State Circuits Conference* (ESSCIRC 2008), pp. 346–349, Sept. 2008.

- [19] V. Gupta, and G. A. Rincon-Mora, "A 5mA 0.6pm CMOS Miller-Compensated LDO Regulator with -27dB Worst-Case Power-Supply Rejection Using 60pF of On-Chip Capacitance," *IEEE International Solid-State Circuits Conference (ISSCC 2011)*, pp. 520-521, Feb. 2007.

- [20] K. N. Leung and P. K. T. Mok, "A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation," *IEEE J. of Solid-State Circuits*, vol. 38, no. 10, pp. 1691–1702, Oct. 2003.

- [21] J. Kitchen et al., "Combined Linear and Δ-Modulated Switch-Mode PA Supply Modulator for Polar Transmitters," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 2, pp. 404-413, Feb. 2009.

- [22] C. Tao and A. Fayed, "PWM Control Architecture With Constant Cycle Frequency Hopping and Phase Chopping for Spur-Free Operation in Buck Regulators," *IEEE Transactions on VLSI*, Vol. 21, No. 9, pp. 1596-1607, Sept. 2013.

- [23] C. Tao and A. Fayed, "A Low-Noise PFM-Controlled Buck Converter for Low-Power applications," *IEEE Transactions on Circuits and Systems I*, vol. 59, no. 12, pp. 3071-3080, Dec. 2012.

- [24] H.-P. Le et Al., "Design Techniques for Fully Integrated Switched-Capacitor DC-DC Converters," *IEEE Journal of Solid-State Circuits*, vol. 46, no. 9, pp. 2120-2131, Sep. 2011.

- [25] L. Chang et al., "Fully-integrated switched-capacitor 2:1 voltage converter with regulation capability and 90% efficiency at 2.3 A/mm2," *IEEE Symposium of VLSI Circuits*, Jun. 2010.

- [26] Y. K. Ramadass and A. P. Chandrakasan, "Voltage scalable switched capacitor DC-DC converter for ultra-low-power on-chip applications," *IEEE Power Electronics Specialists Conf.*, pp. 2353–2359, Jun. 2007.

- [27] G. Patounakis et al., "A fully integrated on-chip DC-DC conversion and power management system," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 3, pp. 443– 451, Mar. 2004.

- [28] W. Kim, D. Brooks, and G-Y Wei, "A Fully-Integrated 3-Level DC-DC Converter for Nanosecond-Scale DVFS," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 1, pp. 206–219, Jan. 2012.

- [29] J. Wibben, R. Harjani, "A High-Efficiency DC-DC Converter Using 2 nH Integrated Inductors," *IEEE Journal of Solid State Circuits*, vol. 43, no. 4, pp. 844-854, April 2008.

- [30] Wei Fu and Ayman Fayed, "A 588MHz Switching Regulator with On-chip Passives and Circuit Stuffing in 65nm," *IEEE, MWSCAS 2014*, accepted.

- [31] S. Abedinpour et al., "A Multistage Interleaved Synchronous Buck Converter with Integrated Output Filter in 0.18 um SiGe Process," *Tran. on Power Electronics*, vol. 22, no. 6, pp. 2164-2175, Nov. 2007.

- [32] N. Sturcken et al., "A Switched-Inductor Integrated Voltage Regulator With Nonlinear Feedback and Network-on-Chip Load in 45 nm SO," *IEEE J. Solid-State Circuits*, vol. 47, no. 8, pp. 1935-1945, Aug. 2012.

- [33] Cheng Huang, Philip K. T. Mok, "An 82.4% Efficiency Package-Bond-wire Based Four-Phase Fully Integrated Buck Converter with Flying Capacitor for Area Reduction," *IEEE Int. Solid-State Circuits Conference (ISSCC 2013)*, pp. 363–364, Feb. 2013.

- [34] W. Kruiskamp, R. Beumer, "Near-Independently Regulated 5-Output Single-Inductor DC-DC Buck Converter Delivering 1.2W/mm2 in 65nm CMOS," *IEEE Int. Solid-State Circuits Conference (ISSCC 2012)*, pp. 274–275, Feb. 2012.

- [35] C.-W. Chen, and A. Fayed, "Dual-Frequency SIMO Power Converters for Low-Power on-Chip Power Grids in SoCs," *IEEE Applied Power Electronics Conf. (APEC 2014)*, Mar. 2014.

- [36] Wei Fu and Ayman Fayed, "A Self-Regulated 588 MHz Buck Regulator with On-chip Passives and Circuit Stuffing in 65nm," *IEEE Midwest symposium on circuits and Systems (MWSCAS 2014)*, Aug. 2014.

- [37] Wei Fu et al., "A DCM-only Buck Regulator with Hysteretic-Assisted Adaptive Minimum-On-time Control for Low-Power Microcontrollers," *Tran. on Power Electronics*, accepted for publication.

# CHAPTER II. ANALYSIS AND MODELING OF LOSSES IN LOW-POWER BUCK REGULATORS

Buck regulators are becoming very popular in low-power System-on-Chip (SoCs), such as microcontrollers, due to their high power conversion efficiency compared to linear counterparts [1]. In these types of SoCs, the maximum load current of the buck regulator is typically less than 50mA, with an output voltage between 0.9V and 1.4V [2]. With such low output power and voltage levels, achieving high efficiency requires careful estimation of the various forms of losses in order to determine the power FET device type and size, the switching frequency, the acceptable accuracy of the passive components, and the routing and package parasitics that can be tolerated. Although several classic loss formulas are readily available in the literature for that purpose [3-5], they are either oversimplified or geared towards high-power high-voltage designs. Thus, they often ignore factors that can be critical in low-power low-voltage designs. For instance, it is common to ignore losses such as transitional losses in the power FETs and dead-time (non-overlap time) body-diode losses. Moreover, since low-power SoCs are usually implemented in low-voltage nanometer CMOS, the buck regulator is typically operated from input voltages that may exceed the gate-tosource voltage rating of its power FETs, and thus, non-rail gate switching using intermediate voltage levels must be employed to preserve device reliability [6], which renders the classic loss formulas inaccurate since they assume rail-to-rail gate switching. Furthermore, with maximum load current of less than 50mA, the regulator operates in DCM most of the time [2], and therefore, using the common CCM-based loss formulas becomes overly pessimistic, and alternative formulas that consider actual DCM operation become necessary for accurate estimation of losses [8]. Additionally, it is also common to simplify gate-drive losses of the

power FETs assuming a lumped gate capacitance without differentiating between  $C_{gs}$  (gate-to-source capacitance) and  $C_{gd}$  (gate-to-drain capacitance), and ignoring how charging/discharging these parasitic capacitors may change other forms of losses such as transitional and conduction losses in the power FETs. While all the above simplifications and omissions can be appropriate for optimizing high-power high-voltage designs, they can lead to significantly sub-optimal design in low-power applications.

In this chapter, the critical components of switching and conduction losses are studied taking the aforementioned factors into consideration. The loss formulas are derived for the CCM and DCM cases separately assuming non-rail gate switching for the sake of generality, but can also be reduced to cover rail-to-rail gate drive as a special case. The formulas can be used for optimizing buck regulators for the best efficiency and aid with determining the dominant loss mechanisms that must be reduced. The paper is organized as follows: chapter 2.1 and 2.2 study the different switching and conduction loss mechanisms and derive the loss formulas in both CCM and DCM, while chapter 2.3 compares the losses estimated by these formulas to the simulated losses in a buck regulator design in 90nm CMOS. Chapter 2.4 concludes this part of the thesis.

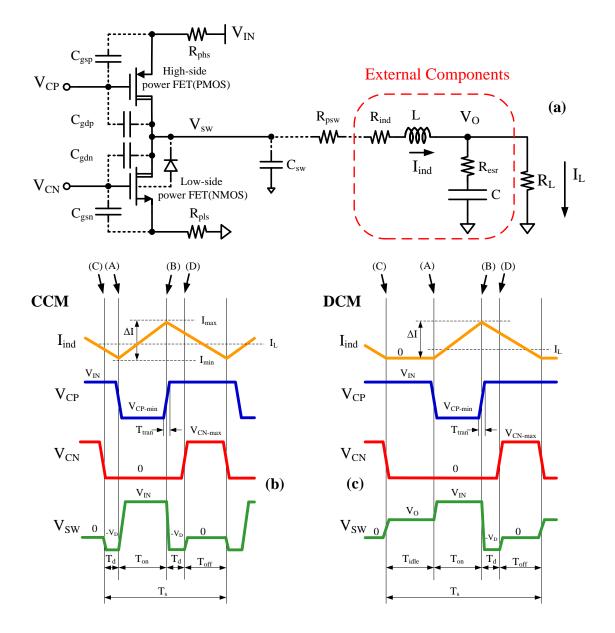

In order to analyze the different losses, the block diagram of a typical buck regulator operating with a switching period  $T_s$ , input and output voltages  $V_{IN}$  and  $V_0$  respectively is shown in Fig. 2.1(a), including all the parasitics critical for losses. The parasitics include the routing and package pin resistances associated with the low-side and high-side power FETs, which are denoted as  $R_{pls}$  and  $R_{phs}$  respectively; the routing and package pin resistances associated with the switching node, which is denoted as  $R_{psw}$ ; and the parasitic resistance associated with the off-chip inductor and capacitor, which are denoted as  $R_{ind}$  and  $R_{esr}$

respectively. The figure also shows the gate-to-source and gate-to-drain capacitances associated with the power FETs, the body-diode associated with the low-side power FET, as well as the total parasitic capacitance associated with the switching node. The special symbols used for the power FETs are to emphasize the case where drain-extended power FETs in nanometer CMOS technologies are used to handle high voltage levels across their drain-source terminals (for instance, 1.8V), while their gate-source voltage levels must continue to be restricted by the low-voltage rating of the FETs (for instance, 1.2V). Fig. 2.1(b) and 2.1(c) show the important voltage and current waveforms in the regulator in CCM and DCM modes respectively. The waveforms emphasize the non-rail gate control levels of the power FETs by showing the swing of the gate control signal V<sub>CP</sub> of the high-side FET between  $V_{CP-min}$  and  $V_{IN}$ , while showing the swing of the gate control signal  $V_{CN}$  of the lowside FET between zero and  $V_{CN-max}$ . The waveforms also show the turn-on voltage  $V_D$  of the body-diode of the low-side power FET. This diode is turned on by the inductor current during the intentionally-inserted dead-time period  $T_d$  at which both the high-side and lowside FETs are kept in an off state to avoid any shoot-through current during transitions. The rise and fall times of all the gate control signals are assumed to be the same and are denoted as  $T_{tran}$ , while  $T_{on}$  and  $T_{off}$  denote the on-time of the high-side and low-side FETs respectively. It is worth noting that both  $T_{tran}$  and  $T_d$  are typically much smaller than  $T_{on}$  and T<sub>off</sub>. In the DCM scenario in Fig. 2.1(c), the additional period of time at which the inductor current is zero and the low-side FET is turned off is denoted as T<sub>idle</sub>. To distinguish between

**Figure 2.1.** (a) A typical buck converter including critical parasitics, and important waveforms in (b) CCM operation, and (c) DCM operation.

the various switching events during the operation of the regulator, these events are denoted in Fig. 2.1(b) and Fig. 2.1(c) as events (A), (B), (C), and (D) for easy reference. Fig. 2.1 will be used frequently throughout the paper while analyzing the various switching and conduction losses.

### 2.1 Switching Losses Analysis

## 2.1.1 Transitional Losses

The first source of switching losses that will be considered is the transitional loss across the power FETs as they transition from a fully on state to a fully off state and vice versa. This loss happens due to the finite rise/fall time of the gate control signals of the FETs and occurs regardless of any switching node capacitance, i.e. it is not associated with charging and discharging the switching node capacitance  $C_{sw}$ . As shown in Fig. 2.1(a) in the CCM case and Fig. 2.1(b) in the DCM case, the transitional losses for the high-side power FET occur during events (A) and (B), while transitional losses for the low-side power FET occur during events (C) and (D). Fig. 2.2 shows a detailed plot of the control signal at the gate of each power FET along with the voltage across the FET and the current flowing through it during each one of the switching events noted in Fig. 2.1. However, for detailed analysis of transitions, each switching event in Fig. 2.1 is further sub-divided in Fig. 2.2 in order to distinguish between different segments within each transition. It is worth observing that since both  $T_{tran}$  and  $T_d$  are normally very short compared to the rate of change in the inductor current, it can be safely assumed that during both events (B) and (D) in Fig. 1 the inductor current stays constant at its peak value I<sub>max</sub>, while during both events (A) and (C) the inductor current stays constant at its trough value I<sub>min</sub>. Note that while Fig. 2.2 describes the CCM case, it can be used for the DCM case by simply assuming that  $I_{min}$  is zero. Starting with the high-side power FET in CCM, Fig. 2.2(a) shows the details of the transition from a fully-off state to a fully-on state (event (A) in Fig. 1(b)). In the first segment of the transition between (A1) and (A2), the gate control signal starts to drop while the FET

continues to be in an off state (the full inductor current continues to flow through the bodydiode of the low-side power FET). The total voltage across the drain-source of the high-side FET is maintained at  $V_{IN} + V_D$  with no current flow, and thus, no significant transitional losses are incurred across it. In the second segment of the transition between (A2) and (A3), the high-side FET starts to turn on and gradual exchange of current between the body-diode of the low-side FET and the high-side FET starts to take place. The current flow in the highside FET can be approximated as a linear transition from zero to I<sub>min</sub>, while the voltage across its drain-source continues to be  $V_{IN} + V_D$  (since the diode is still conducting). Therefore, transitional losses will be incurred across the high-side FET during this segment and can be computed by integrating the product of the constant voltage across the FET and its approximately linear current waveform. In the third segment of the transition between (A3) and (A4), the high-side FET would be bearing the full inductor current  $I_{min}$ , and the body-diode of the low-side FET would be turned off. The drain-source voltage of the highside FET starts to rapidly drop from  $V_{IN} + V_D$  to almost zero (due to the low on-resistance of the high-side FET), and can be approximated as a linear transition. Thus, transitional losses will be incurred across the high-side FET during this segment and can be computed by integrating the product of the constant current through the FET and its approximately linear drain-source voltage waveform. In the fourth segment of the transition between (A4) and (A5), the high-side FET would be bearing the full inductor current with very small voltage across its drain-source. Losses across the FET in this segment are accounted for in the conduction losses in section III and are not considered part of the transitional losses.

Taking the above discussion into consideration, the total transitional losses in the high-side FET during event (A) take place between (A2) and (A4), and can written as:

$$P_{\text{tran}_{\text{HS}_{\text{A}}}} = \frac{\lambda_{\text{p}} \times (V_{\text{IN}} + V_{\text{D}}) \times I_{\text{min}} \times T_{\text{tran}}}{2 \times T_{\text{s}}}$$

(2.1)

where  $\lambda_p$  is the ratio between the period from (A2) to (A4) and the total gate control transition period T<sub>tran</sub>. Therefore the value of  $\lambda_p$  can be between 0 and 1. The actual value of  $\lambda_p$  is inversely proportional to the R<sub>dson</sub> of the high-side FET, which is in turn determined by the FET size, the gate-to-source voltage of the FET when it is turned on, the process corner, and temperature. It is rather easy to determine  $\lambda_p$  through simulations for an existing design. However, since the purpose of the formulas derived in this paper is to aid with initial design decisions,  $\lambda_p$  may not be known in advance. The authors have found that setting  $\lambda_p$  initially to 0.5 is a good starting point for initial estimation of losses, and it can then be tweaked once an initial design is in place to yield more accurate estimation.

The previous analysis applies equally to event (B) shown in Fig. 2.2(b) as the highside FET transitions from a fully-on to fully-off state, except that the current level is at  $I_{max}$ . Therefore, the transitional loss in event (B) can be written as:

$$P_{\text{tran}\_\text{HS}\_B} = \frac{\lambda_p \times (V_{\text{IN}} + V_D) \times I_{\text{max}} \times T_{\text{tran}}}{2 \times T_s}$$

(2.2)

Combining the transitional losses from events (A) and (B), and taking into account the relationship between  $I_{min}$ ,  $I_{max}$ , and the load current  $I_L$ , the total transitional losses across the high-side FET during CCM operation can be written as:

$$P_{\text{tran}\_\text{HS}\_\text{CCM}} = \frac{\lambda_{\text{p}} \times (V_{\text{IN}} + V_{\text{D}}) \times I_{\text{L}} \times T_{\text{tran}}}{T_{\text{s}}}$$

(2.3)

For low-side FET, the turning on transitional profile during event (D) for CCM is shown in Fig. 2.2(c). The whole event starts from (D1) and ends at (D5). Since the voltage level of the switching node stays at  $-V_D$  at the very beginning of (D1), once the gate voltage of the FET ( $V_{CN}$ ) reaches  $V_T - V_D$  at (D2), the FET turns on and it starts to take over the inductor current while the voltage across the FET stays at  $V_D$ . The loss can be computed by assuming a linear transition in the FET's current in this phase. Starting from event (D3), the FET turns into linear region and the voltage across the FET drops to zero until event (D4). During this phase, the loss can be computed by assuming a linear transition in switching node voltage. Therefore, the transitional loss due to turning on NMOS power FET at event (D) can be derived as:

$$P_{\text{tran}\_\text{LS}\_D} = \frac{\lambda_n \times V_D \times I_{\text{max}} \times T_{\text{tran}}}{2 \times T_s}$$

(2.4)

where  $0 < \lambda_n < 1$  represent the ratio of the time between (D2) to (D4) over the whole event (D) duration. Again, the value of  $\lambda_n$  is proportional to the R<sub>dson</sub> of the low-side FET. Note that for low threshold voltage technology, having a diode voltage across the gate and switching node is enough to convert the channel to weak or moderate inversion region. In this scenario, the NMOS channel and its body-diode will provide current simultaneously during the dead-time. Although the transition profile is different comparing to Fig. 2.2(c), a similar conclusion for transitional loss can be derived by applying the same analysis.

The turning off transition of low-side FET during event (C) can be referred to Fig. 2.2(d). The same analysis can be applied to compute the loss during this event and the transitional loss equations are:

$$P_{\text{tran}\_\text{LS}\_\text{C}} = \frac{\lambda_n \times V_D \times I_{\min} \times T_{\text{tran}}}{2 \times T_s}$$

(2.5)

Therefore, the total transitional loss for low-side power FET during CCM operation is:

$$P_{\text{tran}\_\text{LS}\_\text{CCM}} = \frac{\lambda_n \times V_D \times I_L \times T_{\text{tran}}}{T_s}$$

(2.6)

By adding equation (2.3) and (2.6), the total transitional loss for CCM operation can be derived as:

$$P_{\text{tran}\_\text{CCM}} = \lambda \times \frac{(V_{\text{IN}} + 2 \times V_{\text{D}}) \times I_{\text{L}} \times T_{\text{tran}}}{T_{\text{s}}}$$

(2.7)

Where  $\lambda$  equals  $\lambda_n$  and  $\lambda_p$  due to the fact that high-side and low-side power FETs are typically sized as 2:1 ratio so that there on resistance (R<sub>dson</sub>) will be equal to get the optimal efficiency.

For DCM scenarios, the transitional losses only occur during events (B) and (D). The conclusion can be derived by adding equation(2.2) and (2.4) replacing  $I_{max}$  with  $\Delta I$ . Thus, the total transitional loss for DCM operation is:

$$P_{\text{tran}\_\text{DCM}} = \lambda \times \frac{(V_{\text{IN}} + 2 \times V_{\text{D}}) \times \Delta I \times T_{\text{tran}}}{2 \times T_{\text{s}}}$$

(2.8)

Based on equation (2.7) and (2.8), the best way to reduce the transitional loss is to minimize  $T_{tran}$ . However, this will cause reliability and EMI issues for the switching regulator. Thus,  $T_{tran}$  is typically designed based on the trade-off between the efficiency and reliability requirement.

# 2.1.2 Gate & Switching Node Capacitance Losses Estimation

The second source of switching losses is the charging and discharging process of the gate and switching node capacitances of the power FETs. The traditional methodology to compute this kind of losses is based on the equation  $\frac{1}{2}C(V_f - V_i)^2$ , where  $V_i$  and  $V_f$  are the initial and final voltages across the capacitor and *C* is the actual capacitance value. However, this equation assumes the energy discharged on capacitor is 100% lost away and becomes invalid once multiple capacitors are interacting together with other types of losses. For example, the amount of energy discharged at the capacitors during turning on/off power FETs can be transferred to reduce the transitional losses. For this purpose, we will derive the formulas for all the losses during the switching event as a system. The total amount of loss  $E_{loss} = E_{in} - E_{out} - (E_{stored-f} - E_{stored-i})$ , where  $E_{in}$  and  $E_{out}$  represent the amount of energy injected/ejected in-to/out-of the system while  $(E_{stored-f} - E_{stored-i})$  denotes the net change of energy stored in the system. Moreover, we assume the non-rail switching voltage

**Figure 2.2**. A plot of the control signal of each power FET along with the voltage and current across the FET's drain-source terminals during the switching events noted in Fig. 1: (a) high-side FET in event (A), (b) high-side FET in event (B), (c) low-side FET in event (D), and (d) low-side FET in event (C).

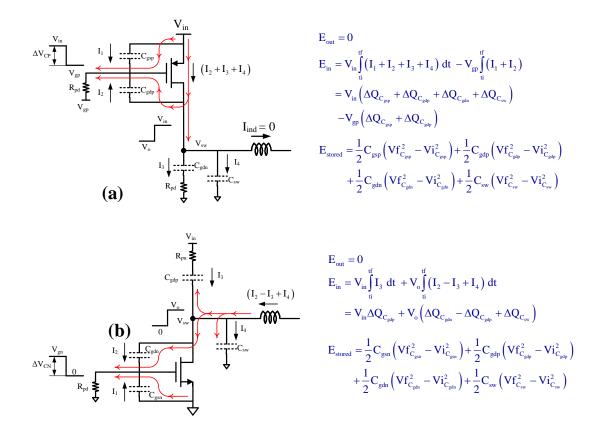

$V_{gp}$  and  $V_{gn}$  are ideal power supplies so as to simplify the derivation. The detailed notifications can be referred to Fig. 2.4 and 2.5. The event by event charge flow plots for CCM scenarios are shown in Fig 2.4, where all the relevant capacitors per event are detailed as well as the current flow of the related capacitors during the event. And the equations for input, output and stored energy are listed at the right hand side of the each event plot. Note that *ti* and *tf* represents and initial and final time of the event and it is essentially the transitional time( $T_{tran}$ ) of the system.

During event (A) where the high-side FET is turning on, the voltage level of the gate of the high-side FET is discharging to  $V_{gp}$  while the switching node is getting charged to  $V_{in}$ . By plug in the initial and final voltage level across the FETs' capacitors in to the equations while understanding that  $\int_{ti}^{tf} (V_{in} - V_{sw}) I_{ind} dt$  is the transitional loss calculated in the previous session. The total capacitive losses during event (A) can be derived as:

$$P_{cap_{ccm}}(A) = \frac{1}{2} \times f_{s} \Big[ C_{gsp} \times \Delta V_{CP}^{2} + C_{gdp} \times (\Delta V_{CP} + V_{in} + V_{BD})^{2} + C_{gdn} \times (V_{in} + V_{BD})^{2} + C_{sw} \times (V_{in} + V_{BD})^{2} \Big]$$

(2.9)

During event (B) where the high-side FET is turning off, the voltage level of the gate of the high-side FET is charging to  $V_{in}$  while the switching node is getting discharged to  $-V_{BD}$ . Based on the energy flow graph denoted on Fig 2.4 (b) and the energy equations listed, the same approach can be taken. The total capacitive losses during event (B) can be derived as:

$$P_{cap\_ccm}(B) = \frac{1}{2} f_s \left[ C_{gsp} \times \Delta V_{CP}^2 - C_{gdp} \times \left[ (V_{in} + V_{BD})^2 - \Delta V_{CP}^2 \right] - C_{gdn} \times \right]$$

$$(V_{in} + V_{BD})^2 - C_{sw} \times (V_{in} + V_{BD})^2$$

(2.10)

Note that the reason why switching loss are negative for  $C_{gdp}$ ,  $C_{gdn}$  and  $C_{sw}$  is due to the fact that the energy discharged at the switching node is not lost but used to compensate part of the switching loss and transitional loss. This is demonstrated in the Fig 2.4(b) with green color as if the discharged energy is feeding back to the supply.

During event (C) where the low-side FET is turning off, the voltage level of the gate of the low-side FET is discharging to 0 while the switching node is getting discharged to  $-V_{BD}$ . The same practice can be done and the total capacitive losses during event (C) can be derived as:

$$P_{cap_{ccm}}(C) = \frac{1}{2} f_s \Big[ C_{gsn} \times \Delta V_{CN}^2 - C_{gdp} \times V_{BD}^2 + C_{gdn} \times (\Delta V_{CN}^2 - V_{BD}^2) - C_{sw} \times V_{BD}^2 \Big]$$

(2.11)

Note that the negative loss part is showing again the equation for the same reason as event (B).

During event (D) where the low-side FET is turning on, the voltage level of the gate of the low-side FET is charging to  $V_{gn}$  while the switching node is getting charged to zero. Based on the energy loss equations detailed in Fig 2.4(d), the total capacitive losses during event (D) can be derived as:

$$P_{cap_{ccm}}(D) = \frac{1}{2} f_s [C_{gsn} \times \Delta V_{CN}^2 + C_{gdp} \times V_{BD}^2 + C_{gdn} \times (\Delta V_{CN} - V_{BD})^2 + C_{sw} \times V_{BD}^2]$$

(2.12)

By combining the equation (2.9) to (2.12), the total capacitive losses in CCM can be derived as:

$$P_{cap\_ccm} = f_s \Big[ C_{gsp} \times \Delta V_{CP}^2 + C_{gsn} \times \Delta V_{CN}^2 + C_{gdp} \times \Delta V_{CP} \times (\Delta V_{CP} + V_{in} + V_{BD}) + C_{gdn} \times \Delta V_{CN} \times (\Delta V_{CN} - V_{BD}) \Big]$$

$$(2.13)$$

One interesting point in equation (2.13) is the loss due to switching node capacitance is out of the equation. However, the switching node capacitance does affect the loss equation in the sense that higher switching node capacitance increases the turning on/off time of the FETs, which will increase the transitional loss of the system.

The capacitive switching loss for DCM can be analyzed with the same methodology and the detailed current flow per event can be referred to Fig 2.5. Note that only event (A) and (C) are illustrated in the figure due to the fact that the event (B) and (C) have the same charge flow diagram and loss equations as the CCM scenario.

During event (A) where the high-side FET is turning on, the same derivation can be applied as the CCM scenario while understanding the transitional loss is zero due to the fact that the inductor current is zero during the high-side FET turning on period. By referring to Fig 2.5(a) and apply some derivations, the capacitive switching loss in event (A) can be arrived as:

$$P_{cap\_dcm}(A) = \frac{1}{2} f_s [C_{gsp} \times \Delta V_{CP}^2 + C_{gdp} \times (\Delta V_{CP} + V_{in} - V_o)^2 + C_{gdn} \times (V_{in} - V_o)^2 + C_{sw} \times (V_{in} + V_o)^2]$$

(2.14)

During event (C) where the low-side FET is turning off in DCM scenario, the inductor current will stay at zero while the switching node oscillates until it settles to  $V_o$ . During this period, the extra energy needed for switching node to oscillate is provided by the output of the converter since both sides of the FETs are turned off. By referring to the equation listed in the figure and plug in the initial and final voltage level across the FETs' capacitors, the total capacitive losses during event (C) can be derived as:

$$P_{cap\_dcm}(C) = \frac{1}{2} f_s [C_{gsn} \times \Delta V_{CN}^2 + C_{gdp} \times V_o^2 + C_{gdn} (\Delta V_{CN} + V_o)^2 + C_{sw} \times V_o^2]$$

(2.15)

By combining the equation (2.10), (2.11), (2.14) and (2.15), the total capacitive losses in DCM can be derived as:

$$P_{cap\_dcm} = f_{s} \Big[ C_{gsn} \times \Delta V_{CP}^{2} + C_{gsn} \times \Delta V_{CN}^{2} + C_{gdp} \times \Delta V_{CP} \times (\Delta V_{CP} + V_{in} + V_{BD}) - C_{gdp} \times [(V_{o} + V_{BD})(\Delta V_{CP} + V_{in}) - V_{o}^{2}] + C_{gdn} \times [\Delta V_{CN} \times (\Delta V_{CN} - V_{BD})] + C_{gdn} \times [\Delta V_{CN}(\Delta V_{CN} + V_{o}) - (V_{o} + V_{BD})(V_{in} + V_{BD} - V_{o})] - C_{sw} \times [V_{in}(V_{o} + V_{BD}) - V_{o}^{2}]$$

(2.16)

Based on the equation, the increasing on switching node capacitance will lead to less capacitive loss. However, this does not count that the increased amount of capacitance will lead to more transitional loss, which will turn out increase the total amount of loss for the system.

**Figure 2.3.** Charge flow diagrams and loss equation derivations for CCM operation for (a) Event A (b) Event B

**Figure 2.4**. Charge flow diagrams and loss equation derivations for CCM operation for (a) Event C (b) Event D

**Figure 2.5**. Charge flow diagrams and loss equation derivations for DCM operation for (a) Event A (b) Event D

2.2 Conduction Losses Analysis

# 2.2.1 Power FETs Conduction Losses Estimation

The conduction losses across the high-side and low-side FETs are estimated only after the FETs have been completely turned on since transitional losses are already accounted for as part of the switching losses. For that purpose, the losses can be estimated as the integral of the square of the current flowing in the FET while it is on, multiplied by its on

resistance. Using the inductor current profile in Fig. 2.1, for CCM scenario, the loss across the high-side FET is  $R_{dson-p}\left(I_L^2 + \frac{\Delta I^2}{12}\right)\left(\frac{T_{on}}{T_s}\right)$  while it is  $R_{dson-n}\left(I_L^2 + \frac{\Delta I^2}{12}\right)\left(\frac{T_{off}}{T_s}\right)$  for the low-side FET[]. Combining these losses, and assuming that  $R_{dson-p} \approx R_{dson-n} = R_{dson}$  (typically the case), and considering  $T_s = T_{on} + T_{off}$ , the total conduction loss can be written as:

$$P_{RFET\_CCM} = R_{dson} \left( I_L^2 + \frac{\Delta I^2}{12} \right)$$

(2.20)

where  $I_L$  is the load current of the converter.

For switching regulators working in DCM scenario, the loss across the high-side FET is  $R_{dson-p}\left(\frac{\Delta I^2}{3}\right)\left(\frac{T_{on}}{T_s}\right)$ , while it is  $R_{dson-n}\left(\frac{\Delta I^2}{3}\right)\left(\frac{T_{off}}{T_s}\right)$  for the low-side FET[]. Combining these losses and taking into account the relationship between  $T_{on}$ ,  $T_{off}$ , and  $T_s$  in DCM operation, the total conduction loss due to power FET can be derived as: